信號的反射

2009/8/9 下午 06:37:50

前面己經介紹過高速訊號的傳遞延滯;

現在讓我們來看看訊號的反射現象。

現在讓我們來看看訊號的反射現象。

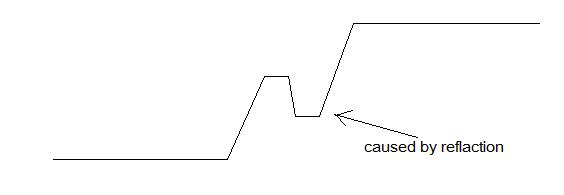

訊號傳遞時可以視為一種波動,

傳遞時如果不能被完全吸收;

這波動就會像波浪打到岸邊後,

傳遞時如果不能被完全吸收;

這波動就會像波浪打到岸邊後,

又以一定的力量反彈回大海。

試想這打回去的浪又跟接著要打上岸的浪結合時會是什麼一種景現!

可能比原要未的使之更深或更張更高。

而這裡所提到的完全吸收,就是一種阻抗匹配。

所以你可以明瞭電路設計中阻抗匹配的重要性了吧!

所以你可以明瞭電路設計中阻抗匹配的重要性了吧!

另外

如果加上傳遞延滯那就更複雜了。

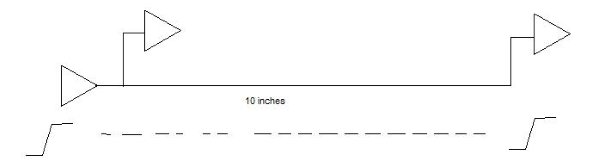

我曾經看過一個設計如下圖:

由於反射現象,我們在靠近訊號驅動器的那一個邏輯閘看到了不正常的雜訊。

這是我們要小心注意的。

要避免這樣的問題,你可以,

在Layout上作一些限制,就是利用EDA工具下 Constrain

或

家一些RC線路去減緩訊號上升時間